![]()

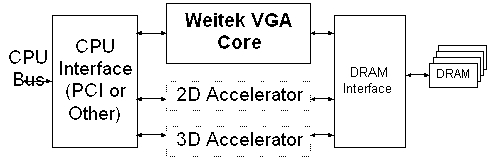

Example Graphics System Configuration

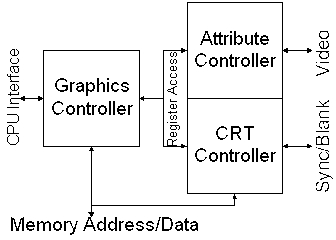

The core has a generic hardware interface to the host interface block and

assumes a 64-bit wide DRAM model of the display buffer. It contains a CRT

controller, an attribute controller and a VGA graphics controller as shown

below. The attribute controller implements a 64 bit wide by 32 deep FIFO for the

display data.

Using Weitek's 0.8um triple layer metal process, the VGA core operates at dot

clock rates up to 135 MHz and memory clocks up to 40 MHz. The CRTC is capable of

reading 64 bits of data every rising edge of memory clock for a peak burst fill

rate of 320 Mbytes/sec.

General Block Diagram

The VGA core supports the following additional functionality over the base level IBM VGA:

![]()

© Copyright 1996, Weitek Corporation. All rights reserved.

Weitek, and the Weitek logo are registered trade marks of Weitek Corporation.

All other trademarks mentioned in the Weitek web pages are the property of their respective owners.

If you have questions or concerns regarding this website, please email the Webmaster.